Image processing is a very heavy computational task, and achieving reasonable throughput is unlikely on conventional architectures. In 1983 an Italian research program was begun for the design, simulation and construction of a multiprocessor image processing system. After a first phase devoted to the comparison of suggested and existing systems and to the definition of a set of benchmarks, a new system was defined.

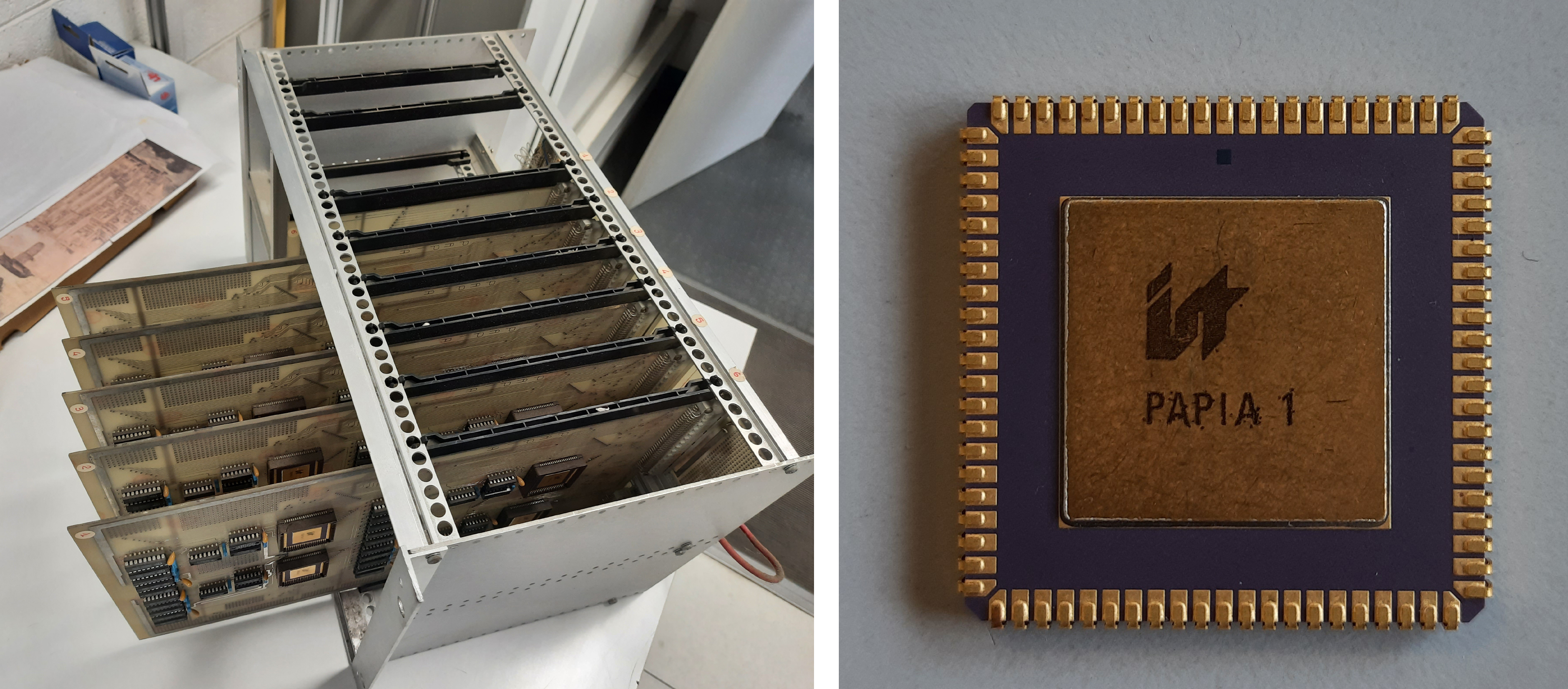

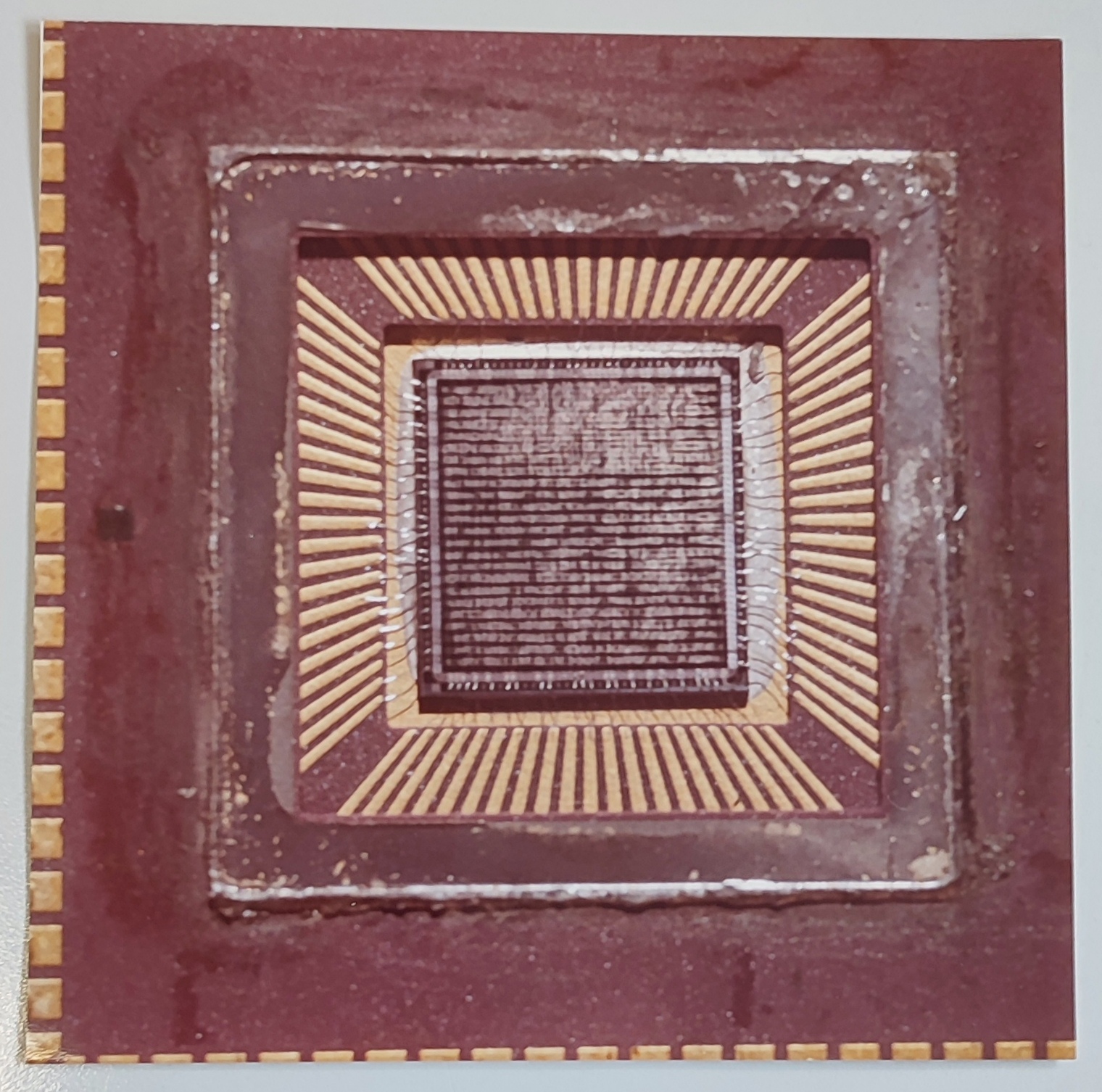

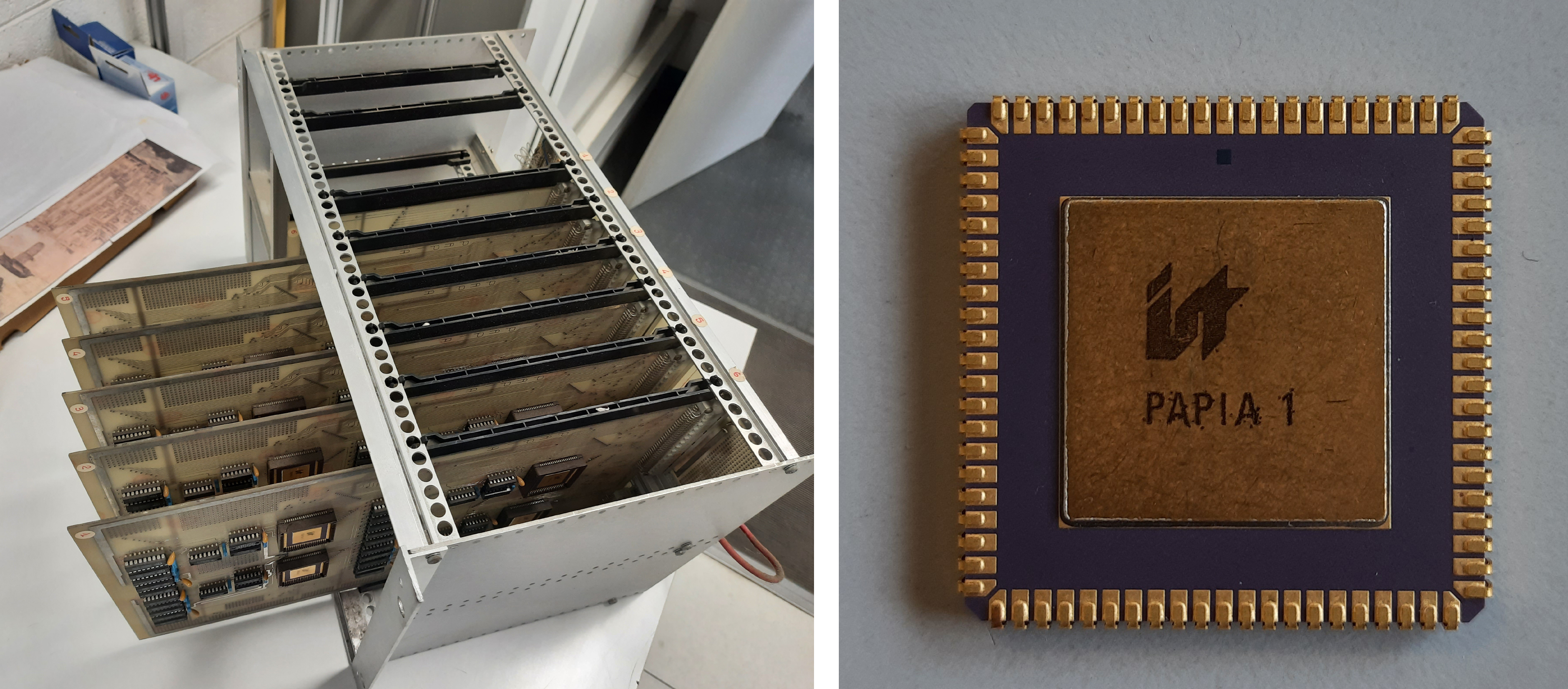

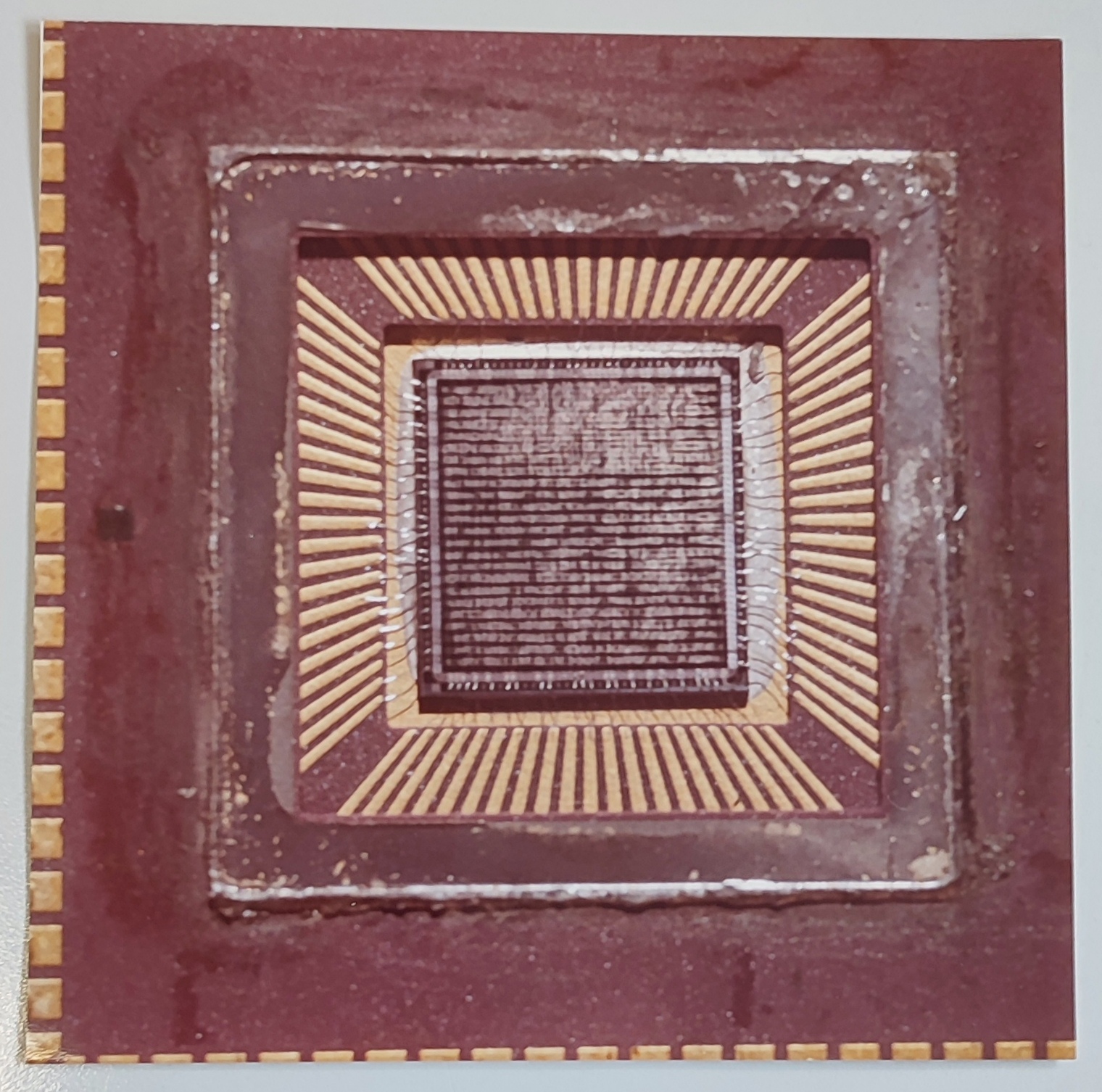

This system was based on a fine-grained pyramid of processors built up by means of a pyramidal cell implemented on a VLSI multiprocessor chip. A first working prototype has been built, the PAPIA 1, a processor array able to reconfigure itself as a pyramid.

The PAPIA 2 array allows a one-to-one mapping between processors and image pixels. A low level and a high level simulator have been developed for the machine. The low-level simulator can execute Papia2 instructions and is used to code and test basic routines. The high-level simulator is devoted to the realization of more complex algorithms using a high level language. The programming environment embeds a source-level debugger to trace running programs and a visualization module to monitor machine status in the form of evolving images. With the 'imget' metaphor, active images capable of modifying their contents, it is possible to offer a high level access to the Papia2 array. Application development can thus ignore hardware details and deal only with image transformations. A solution, with off-the shelf hardware, has also been developed, pursuing the hierarchical implementation of attention mechanisms by multiresolution techniques.

For additional information, please see the article by

Cantoni V., Di Gesù V., Ferretti M., Levialdi S., Negrini R., Stefanelli R., The PAPIA system, Journal of VLSI Signal Processing Systems for Signal, Image and Video Technology 2, pp. 195–217 (1991), DOI:10.1007/BF00925466

describing the peculiarities and the capabilities of the processing element as well as the complete hardware and software system.

Publications

- V. Cantoni, L. Cinque, L. Lombardi, and G. Manzini (1997). Page Segmentation using a Pyramidal Architecture. CAMP '97, pp. 195-199.

- V. Cantoni, L. Lombardi (1995). Hierarchical architectures for Computer Vision. (Keynote lecture) Proc. Euromicro Workshop on Parallel and Distributed Processing, pp.392-398.

- V. Cantoni (1995). Guest Editor: special issue on “Visual Tools for Parallel System Programming”. Journal Visual Language and Computing, Vol.6, No.4, pp.325-326.

- V. Cantoni (1995). Guest Editor: special issue on “New architectural solutions for computer vision systems”. Journal on Machine Vision and Application, Vol.8, pp.77-78.

- V. Cantoni and M. Ferretti (1994). Pyramidal Architectures for Computer Vision. New York, Plenum Press.

- M. Savini, P. Bardoni (1994). Un sistema per elaborazione multi-foveata di immagini. Atti AICA94, pp.1517-1520.

- V. Cantoni, L. Cinque, C. Guerra, L. Levialdi, L. Lombardi (1994). Recognizing 2D-Object by a Multi-Resolution Approach. Proc. XII International Conference on Pattern Recognition, pp.310-316.

- M.G. Albanesi, V. Cantoni, M. Ferretti, F. Mainieri (1994). Progettazione VLSI di un miltiprocessore a piramide virtuale: il chip PAPIA 2. RIDIS - 81/93, Dipartimento di Informatica e e Sistemistica, Università di Pavia.

- M.G. Albanesi, V. Cantoni, M. Ferretti, F. Mainieri (1994). A VLSI 128-Processor Chip for Multiresolution Image Processing. Proc. Conf. on Massively Parallel Computing System.

- V. Cantoni, L. Cinque, C. Guerra, S. Levialdi, L. Lombardi (1993). Tree Pattern Matching for 2D Multiresolution Objects. CAMP 93, pp.43-46.

- V. Cantoni, L. Cinque, C. Guerra, S. Levialdi, L. Lombardi (1993). Un Approccio Linguistico per la Descrizione di Oggetti in Multi-risoluzione. Workshop Conoscenza per Immagini '92, L. Moltedo ed., Il Rostro, pp.173-189.

- V. Cantoni, L. Cinque, C. Guerra, S. Levialdi, L. Lombardi (1993). Describing Object by a Multi-resolution Syntactic Approach. Parallel Image Analysys, A Nakamura, M. Nivat, A. Saudi, P. S. P. Wang, and K. Inoue eds., Springer Verlag, Heidelberg, FRG, pp.54-68.

- A. Biancardi, V. Cantoni, M. Mosconi (1993). Program Development and Coding on a Fine Grained Vision Machine. Machine Vision and Applications, Springer-Verlag, Vol.7 No.1, pp.23-29.

- A. Biancardi, M. Mosconi (1992). Visual Debugging for a Pyramidal Machine. Proc. 11th IAPR International Conference on Pattern Recognition, pp.137-141.

- A. Biancardi, V. Cantoni, M. Mosconi (1992). Un Ambiente Grafico per la Programmazione di una Macchina Piramidale a Grana Fine. Proc. 31st Annual Congress of AICA, pp.230-238.

- A. Biancardi, V. Cantoni, M. Ferretti, M. Mosconi (1992). The PAPIA2 Machine: Hardware and Software Architecture. Proceedings ERCIM Workshop on Parallel Architectures for Computer Vision, Crete, pp.120-141.

- A. Biancardi, V. Cantoni, M. Ferretti, L. Lombardi, M. Mosconi (1992). Processori piramidali per l’elaborazione di immagini. Proc. SIMAI '92, Firenze, pp.114-116.

- V. Cantoni, M. Ferretti, L. Lombardi (1991). Tree Based Multi-Processor Architectures. Proc. Israel/Italy Simposium on Computer Vision, pp.19-30.

- V. Cantoni, M. Ferretti, L. Lombardi (1991). A Comparison of Homogeneous Hierarchical Interconnection Structures. Proc. IEEE, Vol.79 No.4, pp.416-428.

- V. Cantoni, V. Di Gesù, M. Ferretti, S. Levialdi, R. Negrini, R. Stefanelli (1991). The PAPIA System. The Journal of VLSI Signal Processing, Vol.2, pp.195-217.

- V. Cantoni, U. Cei (1991). Hierarchical Parallel Architectures for Image Processing. Int. Workshop on Parallel Computing, D. Marino, G. Mastronardi eds., Acta Press, Anaheim, pp.1-4.

- A. Biancardi, V. Cantoni, U. Cei, M. Mosconi (1991). A Graphical Programming Environment for PAPIA2. Computer Architecture for Machine Perception, CAMP`91, B. Zavidovique, P.L. Wendel eds., pp.123-134.

- M. G. Albanesi, V. Cantoni, U. Cei, M. Ferretti, M. Mosconi (1991). Embedding Pyramids into Mesh Arrays. Reconfigurable SIMD Parallel Processors, H. Li and Q. Stout eds., Prentice Hall, Englewood Cliffs, NJ, pp.123-141.

See also a full list of

Publications