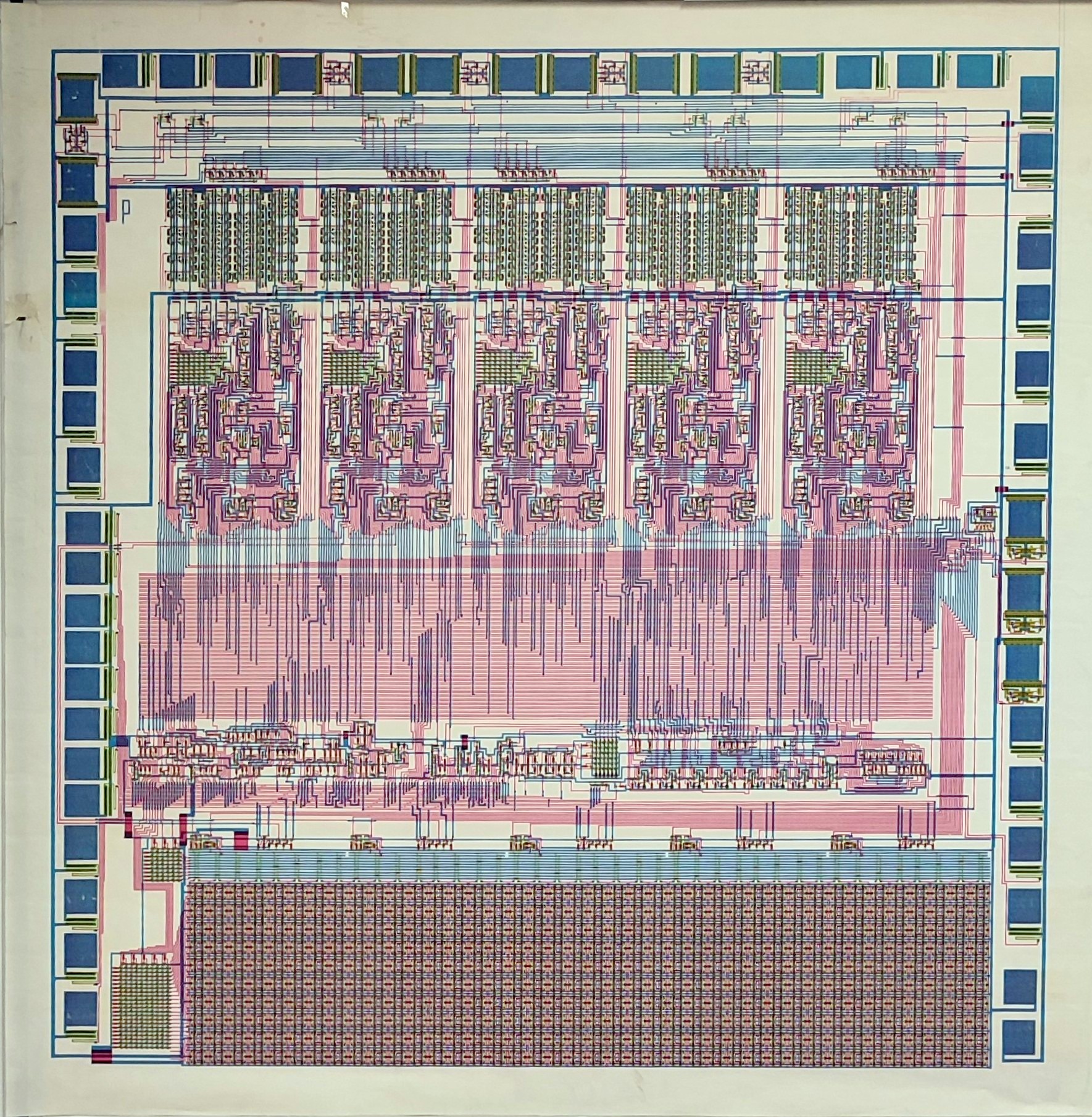

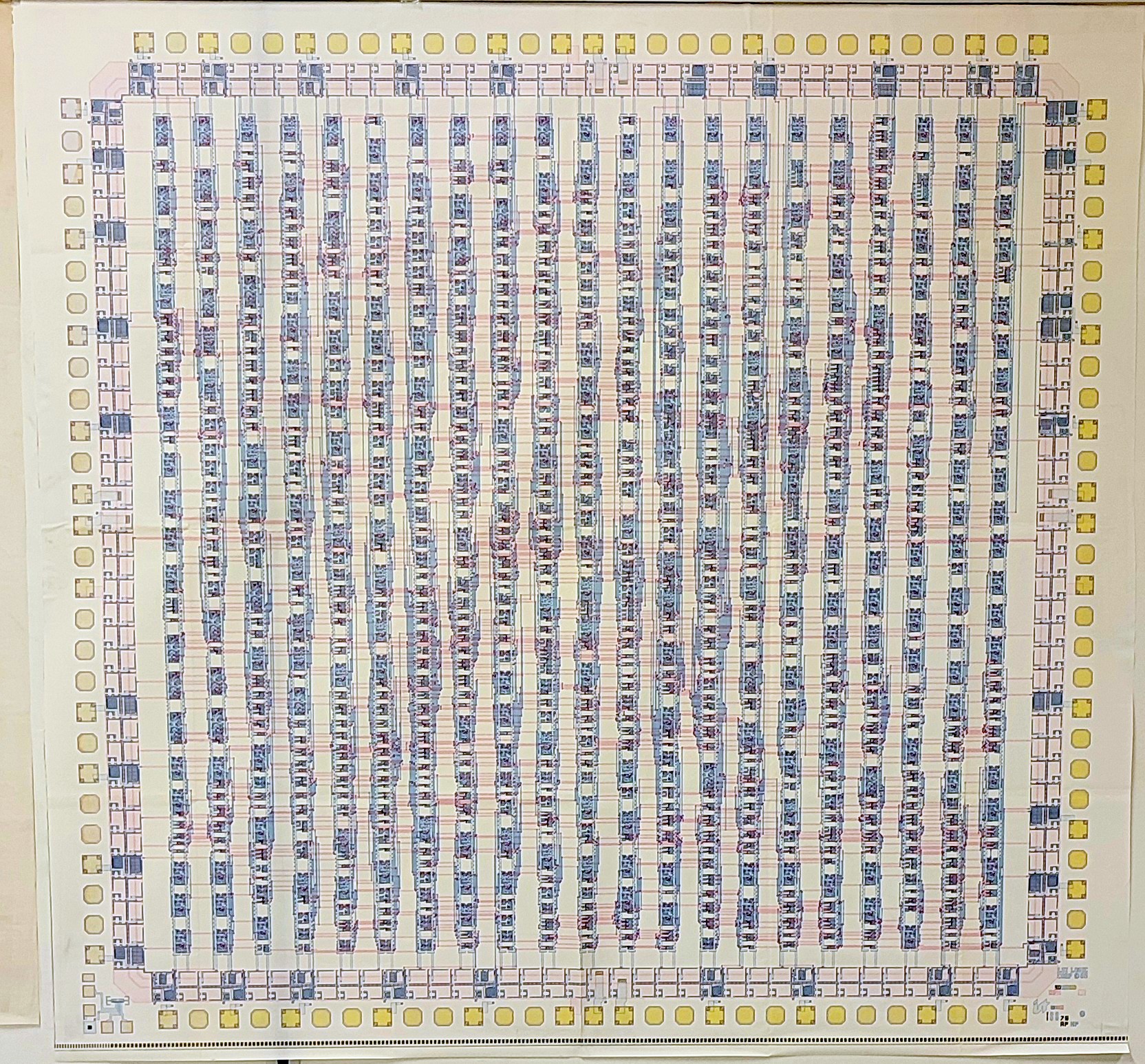

In 1983 an Italian research program was begun for the design, simulation and construction of a multiprocessor image processing system. After a first phase devoted to the comparison of suggested and existing systems and to the definition of a set of benchmarks, a new system was defined. It was based on a fine-grained pyramid of processors built up by means of a pyramidal cell implemented on a VLSI multiprocessor chip. A first working prototype has been built.

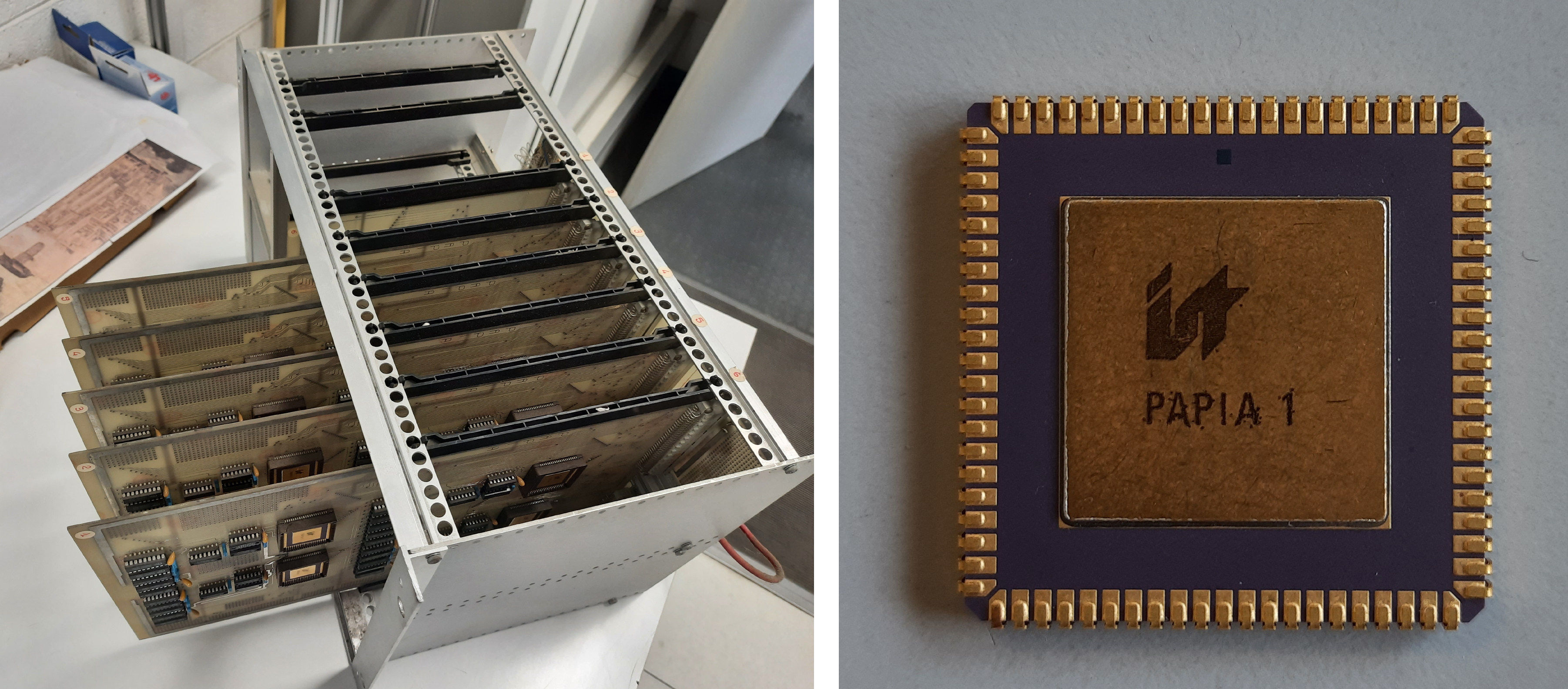

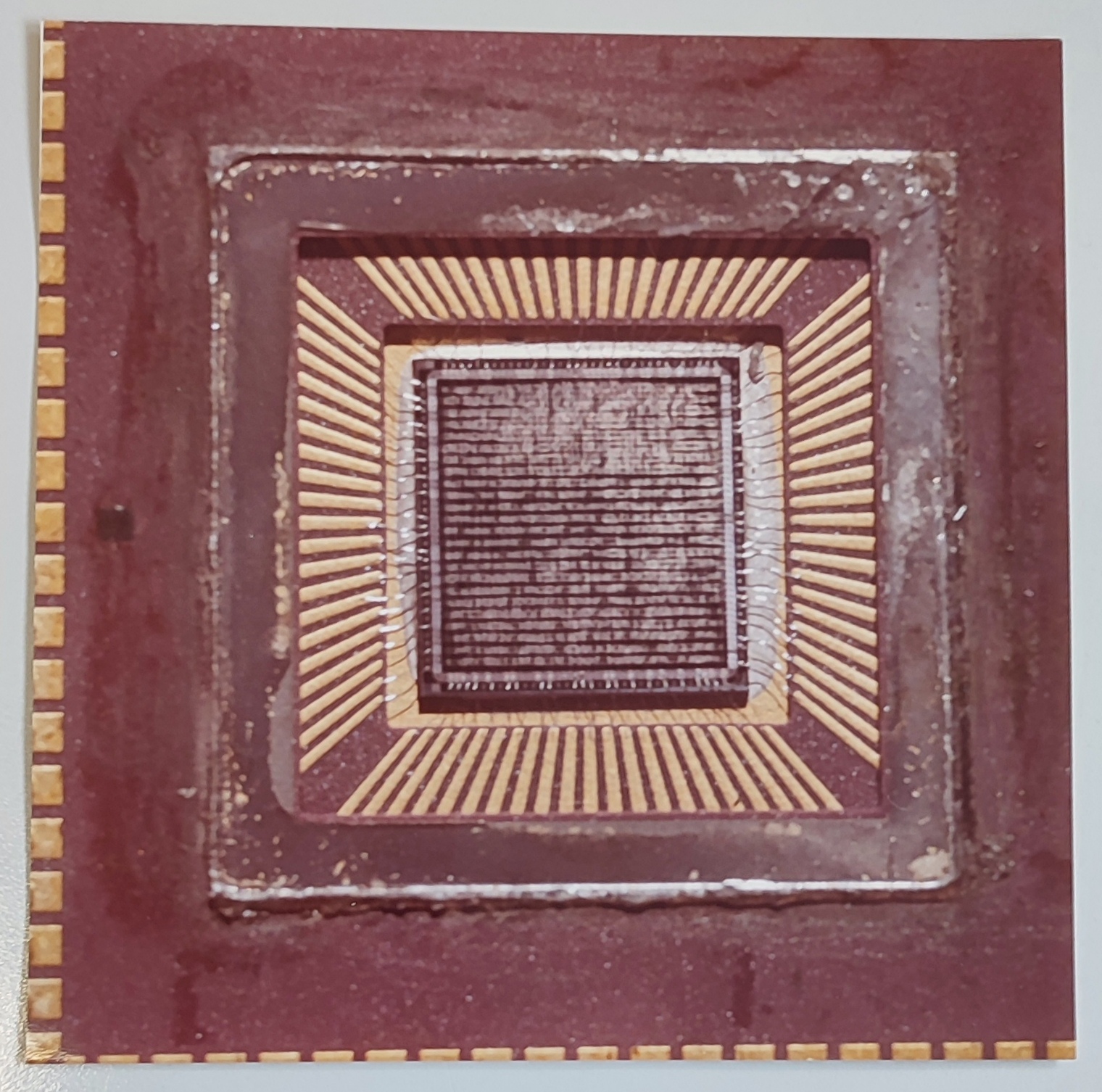

This system was based on a fine-grained pyramid of processors built up by means of a pyramidal cell implemented on a VLSI multiprocessor chip. A first working prototype has been built, the PAPIA 1, a processor array able to reconfigure itself as a pyramid.

The PAPIA 2 array allows a one-to-one mapping between processors and image pixels. A low level and a high level simulator have been developed for the machine. The low-level simulator can execute Papia2 instructions and is used to code and test basic routines. The high-level simulator is devoted to the realization of more complex algorithms using a high level language. The programming environment embeds a source-level debugger to trace running programs and a visualization module to monitor machine status in the form of evolving images. With the 'imget' metaphor, active images capable of modifying their contents, it is possible to offer a high level access to the Papia2 array. Application development can thus ignore hardware details and deal only with image transformations. A solution, with off-the shelf hardware, has also been developed, pursuing the hierarchical implementation of attention mechanisms by multiresolution techniques.

For additional information, please see the article by

Cantoni V., Di Gesù V., Ferretti M., Levialdi S., Negrini R., Stefanelli R., The PAPIA system, Journal of VLSI Signal Processing Systems for Signal, Image and Video Technology 2, pp. 195–217 (1991), DOI:10.1007/BF00925466

describing the peculiarities and the capabilities of the processing element as well as the complete hardware and software system.

Laboratorio di Visione Artificiale e Multimedia

Dipartimento di Ingegneria Industriale e dell’Informazione

Università di Pavia

Via Ferrata 5, 27100 Pavia - ITALY

+39 0382 98 5372/5486

web-vision@unipv.it