### Synchronous Sequential Circuit

- ✓ The change of internal state occurs in response to the synchronized clock pulses.

- ✓ Data are read during the clock pulse (e.g. rising-edge triggered)

- It is supposed to wait long enough after the external input changes for all flip-flop inputs to reach a steady value before the next clock pulse

- ✓ Unsuitable Situations:

- Inputs can change at any time and cannot be synchronized with a clock

- Circuit is large, a cost in time of transitions can not be avoided

### Asynchronous Circuits

- ✓ Not synchronized by a common clock

- ✓ States change immediately after input changes

- ✓ For a given value of input variables, the system is stable if the circuit reaches a steady state condition.

- $\checkmark$  The circuit reaches a steady-state condition when  $y_i = Y_i$  for all i.

- A transition from one stable state to another occurs only in response to a change in an input variable

- Fundamental-mode operation

- The input signals change only when the circuit is in a stable condition

- The input signals change one at a time

- ✓ The time between two input changes must be longer than the time it takes the circuit to reach a stable state.

- Timing is a Major Problem because of unequal delays through various paths in the circuit

## Why Asynchronous Sequential Circuits?

#### Asynchronous sequential circuits basics

- ✓ No clock signal is required

- Internal states can change at any instant of time when there is a change in the input variables

- ✓ Have better performance but hard to design due to timing problems

#### Why Asynchronous Circuits?

- Accelerate the speed of the machine (no need to wait for the next clock pulse).

- $\checkmark$  Simplify the circuit in the small independent gates.

- ✓ Necessary when having multi circuits each having its own clock.

#### Analysis Procedure

The analysis consists of obtaining a table or a diagram that describes the sequence of internal states and outputs as a function of changes in the input variables.

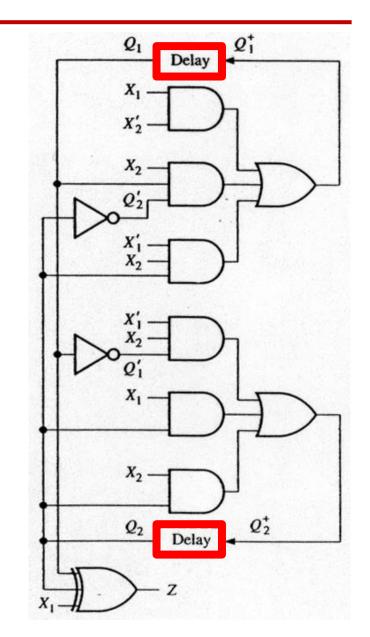

## Example Circuit

- ✓ First construction of Asynchronous Circuits:

- using only gates

- with feedback paths

- ✓ Analysis:

- Lump all of the delay associated with each feedback path into a "delay" box

- Associate a state variable with each delay output

- Construct the flow table

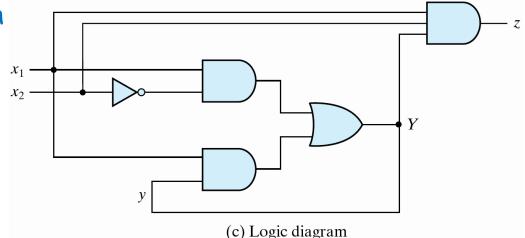

- ✓ Network equations

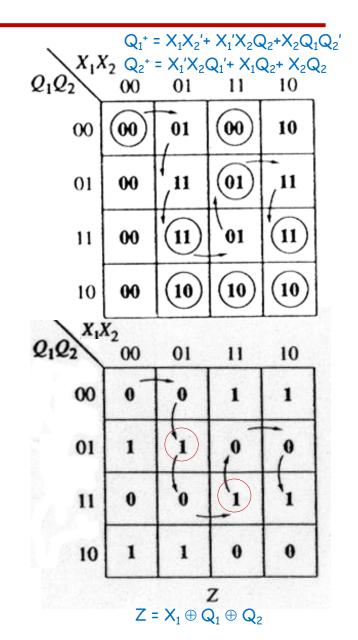

- $Q_{1}^{+} = X_{1}X_{2}' + X_{1}'X_{2}Q_{2} + X_{2}Q_{1}Q_{2}'$  $Q_{2}^{+} = X_{1}'X_{2}Q_{1}' + X_{1}Q_{2} + X_{2}Q_{2}$  $Z = X_{1} \oplus Q_{1} \oplus Q_{2}$

## Example Circuit: Output Table

- ✓ 1. Starting in total state

X<sub>1</sub>X<sub>2</sub>Q<sub>1</sub>Q<sub>2</sub>=0000

- ✓ 2. Input changes to 01

- Internal state changes to 01 and then to 11.

- ✓ 3. Input changes to 11.

- Go to unstable total state 1111 and then to 1101.

- $\checkmark$  4. Input changes to 10.

- Go to unstable total state 1001 and then to 1011.

- $\checkmark$  The output sequence:

- $\underbrace{\mathbf{0}(0)}_{(0)}(1) \, \mathbf{0}(1) \, \underbrace{\mathbf{0}(0)}_{(0)} \, \mathbf{1}$

- Condensed to the form

0 (1) 0 (1) 0 1.

- Two transient 1 outputs is dangerous can be eliminated by proper design.

- Transition table is useful to analyze an asynchronous circuit from the circuit diagram. Procedure to obtain transition table:

- 1. Determine all feedback loops in the circuits

- 2. Mark the input  $(y_i)$  and output  $(Y_i)$  of each feedback loop

- 3. Derive the Boolean functions of all Y's

- 4. Plot each Y function in a map and combine all maps into one table (flow table)

- 5. Circle those values of Y in each square that are equal to the value of y in the same row (stable states)

#### Asynchronous Sequential Analysis

#### Asynchronous Sequential Analysis

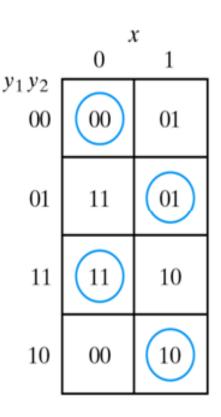

## Asynchronous Sequential Analysis

Asynchronous Sequential Circuit

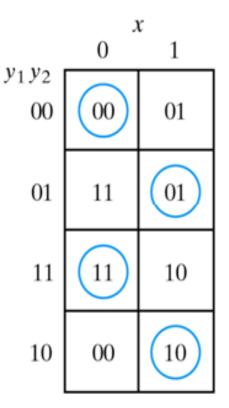

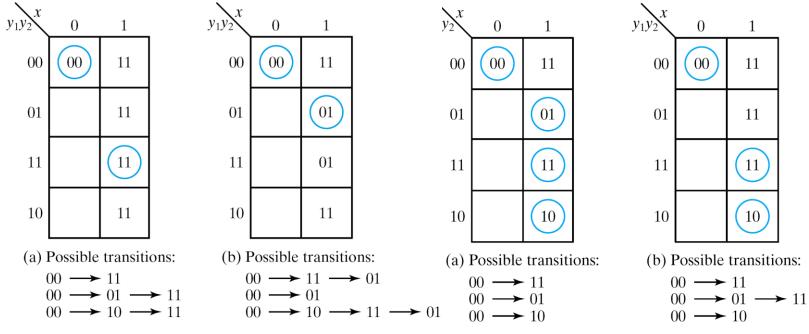

$\checkmark$  The state variables:  $Y_1$  and  $Y_2$

•

$$Y_1 = xy_1 + \overline{x}y_2$$

•  $Y_2 = x\overline{y}_1 + \overline{x}y_2$

$Y_1 = xy_1 + x'y_2$

Combine the internal state with input variables Stable total states:  $Y_1 = xy_1 + \overline{x}y_2$  $\mathbf{Y}_2 = \mathbf{x}\overline{\mathbf{y}}_1 + \overline{\mathbf{x}}\mathbf{y}_2$  $y_1y_2x = 000, 011, 110 \text{ and } 101$ х х х  $y_1 y_2$  $y_1 y_2$ *y*<sub>1</sub>*y*<sub>2</sub> (a) Map for

(b) Map for  $Y_2 = xy'_1 + x'y_2$

- In an asynchronous sequential circuit, the internal state can change immediately after a change in the input.

- It is sometimes convenient to combine the internal state with input value together and call it the Total State of the circuit. (Total state = Internal state + Inputs)

- $\checkmark\,$  In the example , the circuit has

- 4 stable total states: (y<sub>1</sub>y<sub>2</sub>x= 000, 011, 110, and 101)

- 4 unstable total states: (y<sub>1</sub>y<sub>2</sub>x= 001, 010, 111, and 100)

- ✓ If y=00 and x=0⇒Y=00 (Stable state)

- ✓ If x changes from 0 to 1 while y=00, the circuit changes Y to 01 which is temporary unstable condition (Y≠y)

- ✓ As soon as the signal propagates to make Y=01, the feedback path causes a change in y to 01. (transition form the first row to the second row)

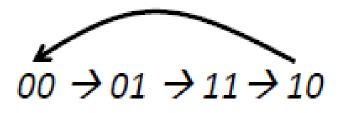

- ✓ If the input alternates between 0 and 1, the circuit will repeat the sequence of states:

### Flow Table

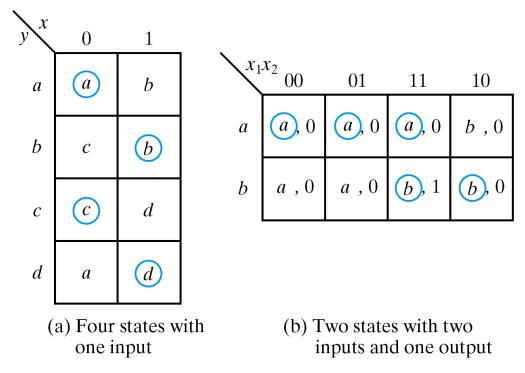

- A flow table is similar to a transition table except that the internal state are symbolized with letters rather than binary numbers.

- ✓ It also includes the output values of the circuit for each stable state.

### Flow Table

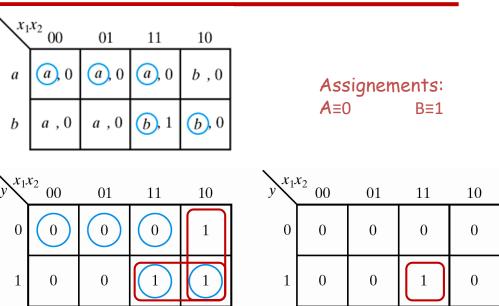

✓ In order to obtain the circuit described by a flow table, it is necessary to convert the flow table into a transition table from which we can derive the logic diagram. a = aa = aa

This can be done through the assignment of a distinct binary value to each state.

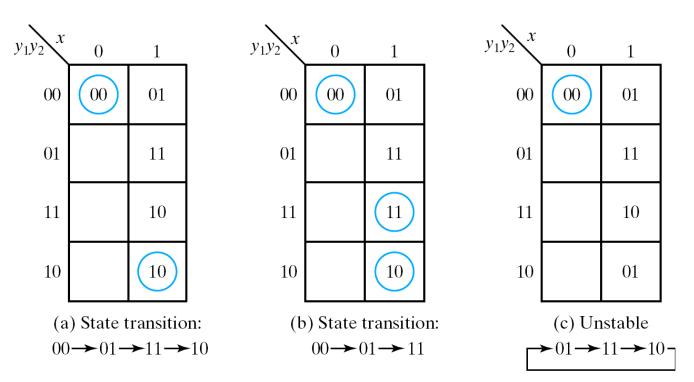

# Race condition

- Two or more binary state variables will change value when one input variable changes.

- ✓ Cannot predict state sequence if unequal delay is encountered.

- Non-critical race: The final stable state does not depend on the change order of state variables

- Critical race: The change order of state variables will result in different stable states. Must be avoided !!

### Race Solution

- ✓ It can be solved by making a proper binary assignment to the state variables.

- ✓ The state variables must be assigned binary numbers in such a way that only one state variable can change at any one time when a state transition occurs in the flow table.

### Stability Check

- Asynchronous sequential circuits may oscillate between unstable states due to the feedback

- Must check for stability to ensure proper operations

- $\checkmark$  Can be easily checked from the transition table

- Any column has no stable states  $\longrightarrow$  unstable Ex: when  $x_1x_2=11$  in (b), Y and y are never the same

(b) Transition table

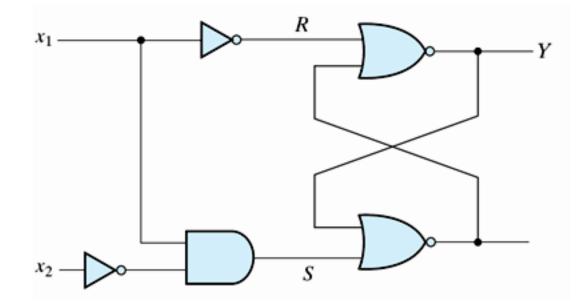

### Latches in Asynchronous Circuits

- ✓ The traditional configuration of asynchronous circuits is using one or more feedback loops

- No real delay elements.

- ✓ It is more convenient to employ the SR latch as a memory element in asynchronous circuits

- Produce an orderly pattern in the logic diagram with the memory elements clearly visible.

- ✓ SR latch is an asynchronous circuit

- So will be analyzed first using the method for asynchronous circuits.

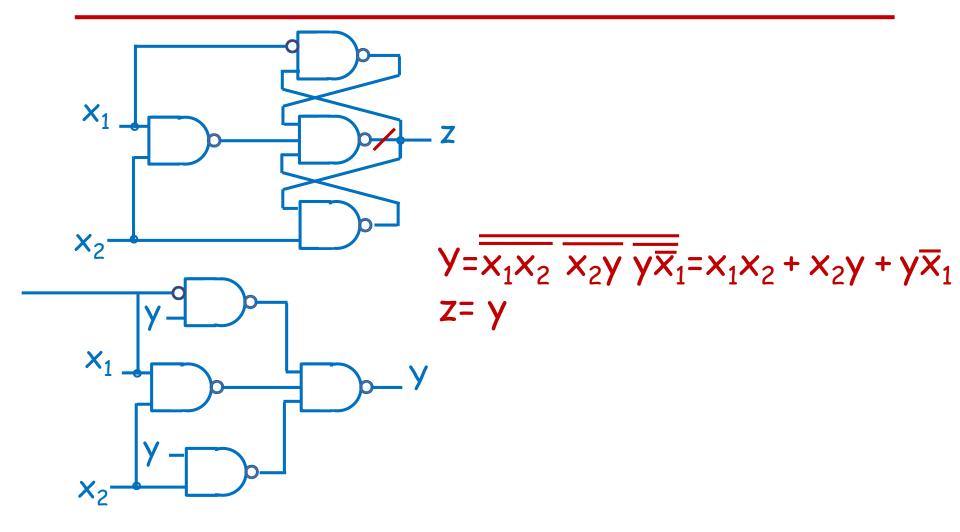

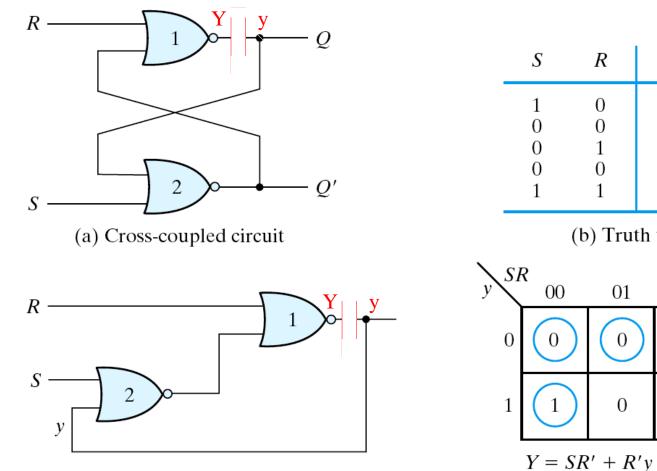

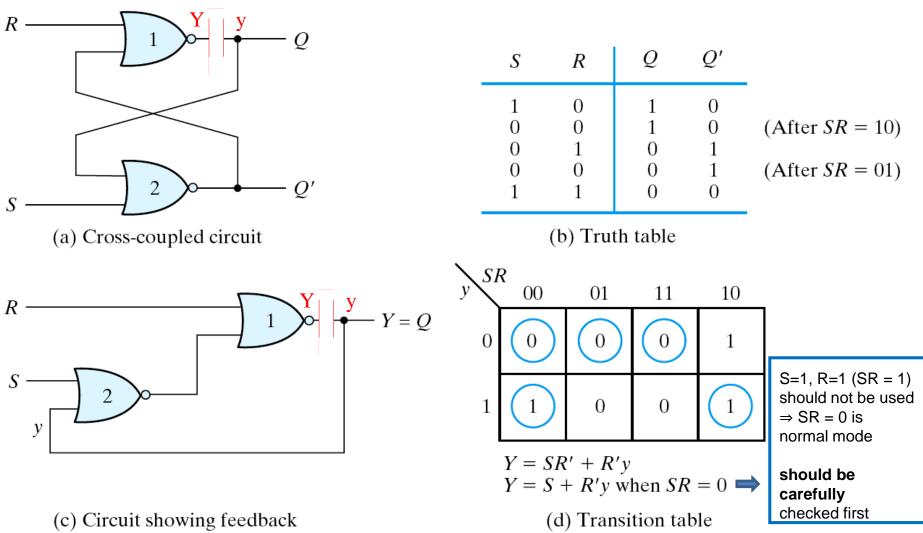

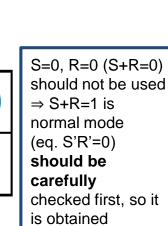

### SR Latch with NOR Gates

(c) Circuit showing feedback

(b) Truth table

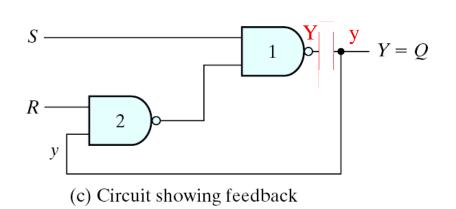

#### (d) Transition table

The condition to be avoided is that both S and R inputs must not be 1 simultaneously. This condition is avoided when SR = 0 (i.e., ANDing of S and R must always result in 0).

When SR = 0 holds at all times, the excitation function derived previously:

$$Y = SR' + R'y$$

can be expressed as:

$$Y = S + R'y$$

#### SR Latch with NOR Gates

Circuit showing recuback

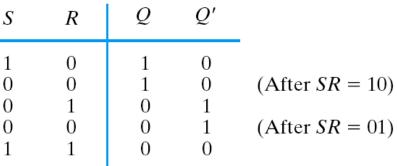

#### SR Latch with NAND Gates

| S                                                                                            | R                     | Q                     | Q'                                                                                           |  |

|----------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------------------------------------------------------------------------------|--|

| $     \begin{array}{c}       1 \\       1 \\       0 \\       1 \\       0     \end{array} $ | 0<br>1<br>1<br>1<br>0 | 0<br>0<br>1<br>1<br>1 | $     \begin{array}{c}       1 \\       1 \\       0 \\       0 \\       1     \end{array} $ |  |

(After SR = 10) (After SR = 01)

01

$\sum_{y} SR$

0

1

00

11

10

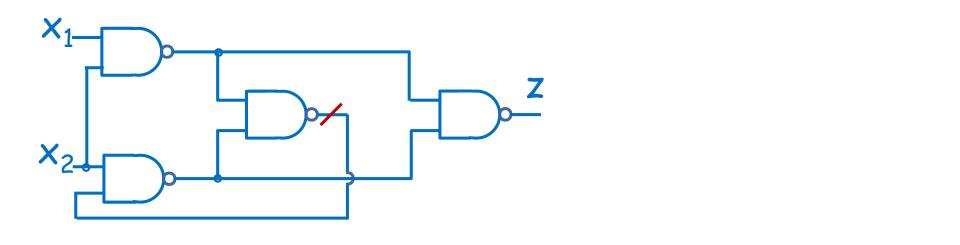

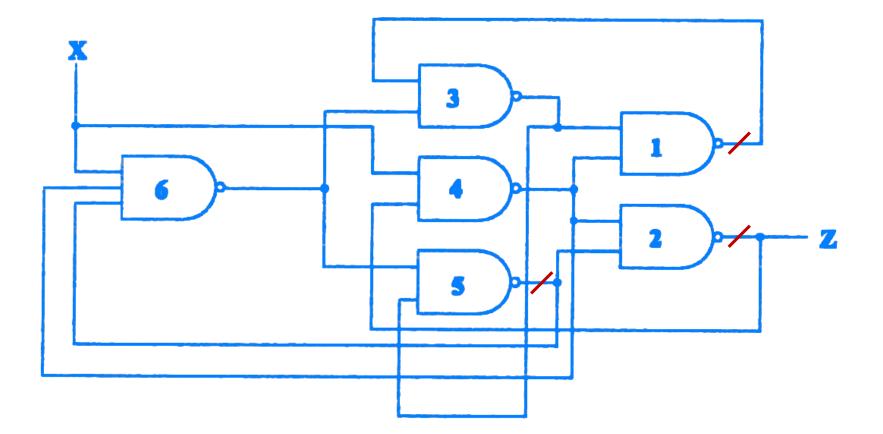

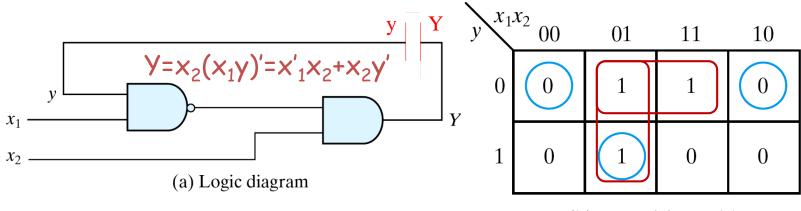

Analysis Example

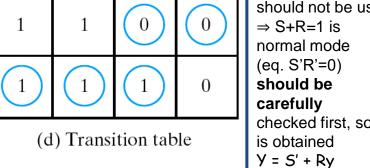

## Analysis Example

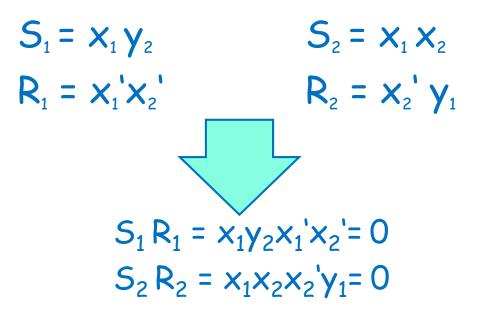

- The procedure for analyzing an asynchronous sequential circuit with SR latches can be summarized as follows:

- Label each latch output with  $Y_i$  and its external feedback path with  $y_i$  for i=1,2,...,k

- Derive the Boolean functions for the  $S_i$  and  $R_i$  inputs in each latch.

### Analysis Example

Check whether SR =0 for each NOR latch or whether S'R' = 0 for each NAND latch. (if either of these two conditions is not satisfied, there is a possibility that the circuit may not operate properly)

> $S_1 R_1 = x_1 y_2 x_1' x_2' = 0$  $S_2 R_2 = x_1 x_2 x_2' y_1 = 0$

Evaluate Y = S + R'y for each NOR latch or Y = S' + Ry for each NAND latch.

$$Y_{1} = S_{1} + R_{1}' y_{1} = x_{1}y_{2} + x_{1}y_{1} + x_{2}y_{1}$$

$$Y_{2} = S_{2} + R_{2}' y_{2} = x_{1}x_{2} + x_{2}y_{2} + y_{1}'y_{2}$$

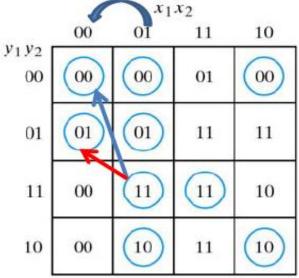

## Analysis Example

- Construct a map, with the y's representing the rows and the x inputs representing the columns.

- Plot the value of  $Y=Y_1Y_2...Y_k$  in the map.

- Circle all stable states such that Y=y. The result is then the transition table.

- The transition table shows that the circuit is **stable**

- Race Conditions: there is a **critical race** condition when the circuit is initially in total state  $y_1y_2x_1x_2 = 1101$  and  $x_2$  changes from 1 to 0.

- The circuit should go to the total state <u>0000</u>.

- If  $Y_1$  changes to 0 before  $Y_2$ , the circuit goes to total state 0100 instead of 0000.

**Transition Table**

$Y_1 = x_1y_2 + x_1y_1 + x_2y_1$  $Y_2 = x_1x_2 + x_2y_2 + y_1'y_2$

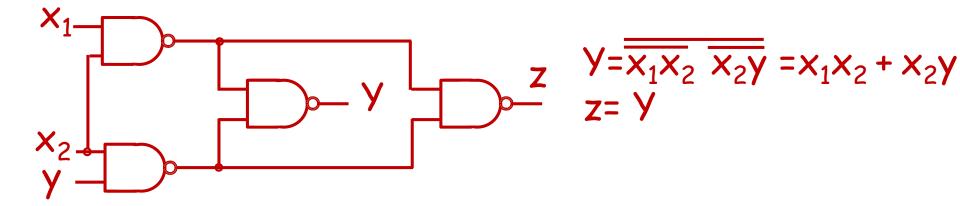

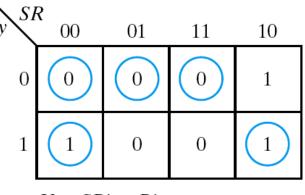

## **Implementation** Procedure

- Procedure to implement an asynchronous sequential circuits with SR latches:

- Given a transition table that specifies the excitation function  $Y = f(y_1, -, y_n, x_1, -, x_m)$  derive a pair of maps for each  $S_i$  and  $R_i$  using the latch excitation table

- Derive the Boolean functions for each S<sub>i</sub> and R<sub>i</sub> (do not to make S<sub>i</sub> and R<sub>i</sub> equal to 1 in the same minterm square; for NAND latch, use the complemented values)

- Draw the logic diagram using k latches together with the gates required to generate the S and R

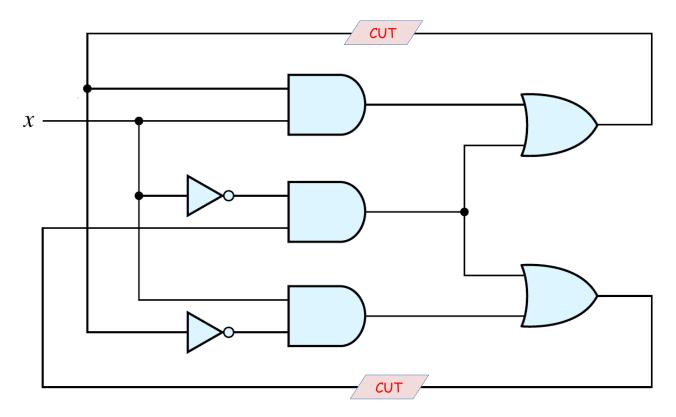

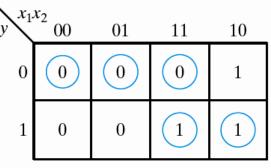

## Implementation Example

- ✓ Given a transition table  $Y = f(y_1, -, y_n, x_1, -, x_m)$ , then the general procedure for implementing a circuit with SR latches is specified by the excitation function, and can be summarized as follows:

- Given a transition table

(a) Transition table

- $Y = x_1 x'_2 + x_1 y$

- Determine the Boolean functions for the S and R inputs of each latch (this is done by using the latch excitation table)

## Implementation Example

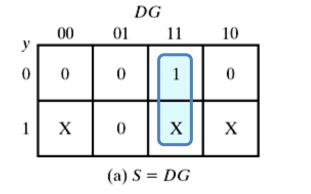

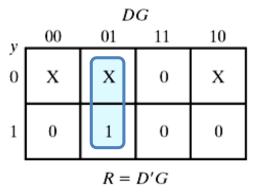

• From maps: the simplified Boolean functions are

$$S = x_1 x_2'$$

and  $R = x_1'$  > NOR latch

Check whether SR=0 for each NOR latch or whether S'R'=0 for each NAND latch:

$SR = x_1 x_2 x_1' = 0$

• Draw the logic diagram, using k latches together with the gates required to generate the S and R Boolean functions obtained in step1 (for NAND latches, use the complemented values)

- Primitive flow table has exactly one stable total state (internal state + input) per row

- $\checkmark$  To avoid the timing problems:

- Only one input variable changes at a time

- Networks reach a stable total state between input changes (Fundamental Mode)

- ✓ Every change in input changes the state

## Design procedure

- 1. Obtain a primitive table from specifications

- 2. Reduce flow table by merging rows in the primitive flow table

- 3. Assign binary state variables to each row of reduced table

- 4. Assign output values to dashes associated with unstable states to obtain the output map

- 5. Simplify Boolean functions for excitation and output variables;

- 6. Draw the logic diagram

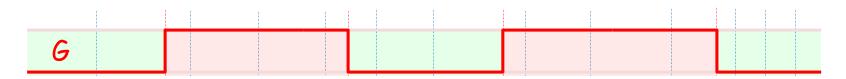

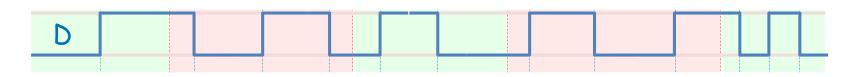

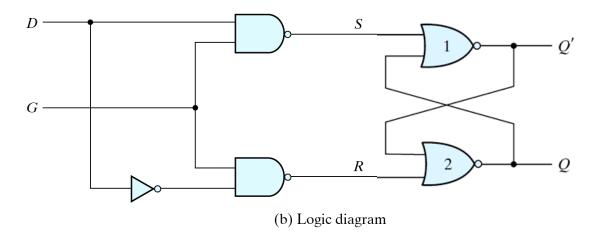

- ✓ Problem Statement:

- Design a gated latch circuit (memory element) with two inputs, G(gate) and D(Data) and one output Q.

- The Q output will follow the D input as long as G=1. When G goes to O, the information that was present at the D input at the time of transition is retained at the Q output.

- Q = D when G =1

- Q retains its value when G goes to 0

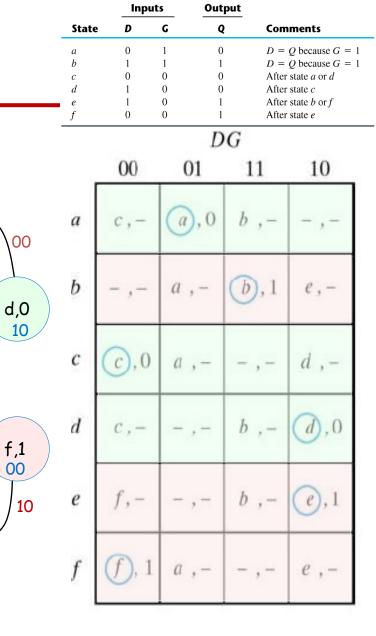

| 1-Primitive Flow Table                                                  |           | Inputs |         | Output |                                  |

|-------------------------------------------------------------------------|-----------|--------|---------|--------|----------------------------------|

| <ul> <li>A primitive flow table is a flow table</li> </ul>              | State     | D      | G       | Q      | Comments                         |

| with only one stable total state (interne                               |           | 0      | 1       | 0      | D = Q because $G = 1$            |

| state + input) in each row.                                             | b         | 1      | 1       | 1      | D = Q because $G = 1$            |

| In order to form the primitive flow                                     | С         | 0      | 0       | 0      | After state <i>a</i> or <i>d</i> |

| table, we first form a table with all                                   | d         | 1      | 0       | 0      | After state c                    |

| •                                                                       | е         | 1      | 0       | 1      | After state $b$ or $f$           |

| possible total states, combinations of                                  | f         | 0      | 0       | 1      | After state <i>e</i>             |

| the inputs and internal states, simultaneous transitions of two inputva | riables ( | are no | t allow | red    |                                  |

c,0

00

10

11

01

00

00

a,0

01

b,1

11

11

$\mathbf{\Lambda}$

10

e,1

10

11

01

#### 1-Primitive Flow Table

- One square in each row is a stable state for that row.

- First, we note that both inputs are not allowed to change at the same time.

- We enter dash marks in each row that differs in two or more variables from the input variables associated with the stable state.

- Next it is necessary to find values for the two squares adjacent to the stable state in each row.

- the previous table may support in deriving the necessary information.

- All outputs associated with unstable states are don't care conditions

- We marked them with a dash.

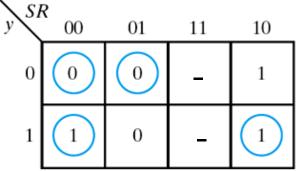

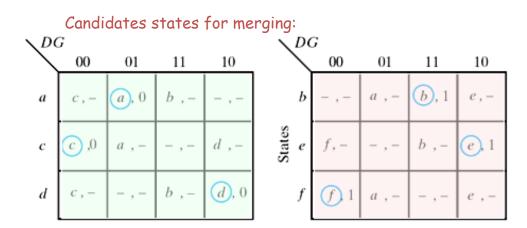

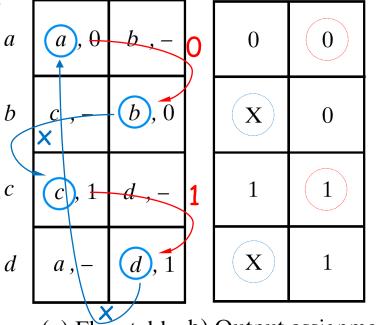

#### 2-Reduction of the Primitive Flow Table

• Two or more rows can be merged into one row if there are non-conflicting states and outputs in every columns.

- After merged into one row:

- Don't care entries are overwritten

- Stable states and output values are included

- A common symbol is given to the merged row

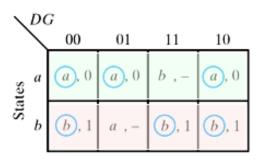

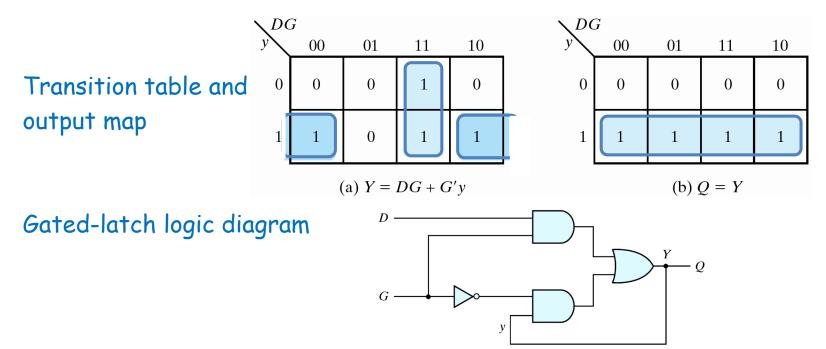

#### **3-Transition Table and Logic Diagram**

- ✓ In order to obtain the circuit described by the reduced flow table, it is necessary to assign a distinct binary value to each state.

- $\checkmark$  This converts the flow table to a transition table.

- ✓ A binary state assignment must be made to ensure that the circuit will be free of critical race.

#### a=0, b=1 in this example

#### 4. Implementation with SR Latch

#### Circuit with SR latch

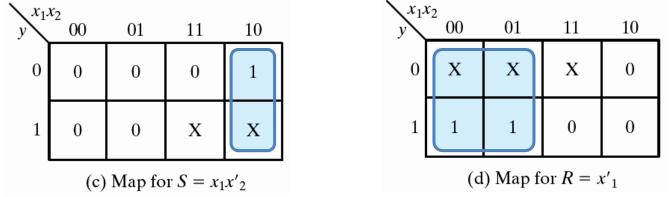

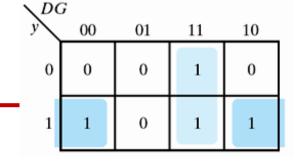

#### 5- Assigning Outputs to Unstable States

- ✓ While the stable states in a flow table have specific output values associated with them, the unstable states have unspecified output entries designated by a dash.

- These unspecified output values must be chosen so that no momentary false outputs occur when the circuit switches between stable states.

- If the two stable states have the save output value, then an unstable states that are a transient state between them must have the same output.

- If an output variable is to change as a result of a state change, then this variable is assigned a don't care condition\*.

#### 5- Assigning Outputs to Unstable States

Example:

If a changes to b, the two stable states have the same output value =0 (0=>0: 0) a the transient unstable state b in the first row must have the same output value = 0

if c changes to d same for  $1 \Rightarrow 1$ : 1

If b changes to c, the two stable states<sup>c</sup> have different output values 0⇒1: x

the transient unstable state c in the d second row is assigned a don't care condition

if d changes to a same for  $1 \Rightarrow 0: x$

(a) Flow table b) Output assignment